�߾�����Ƶ��λsigma-delta���������

ʯ����1, 2��������1�����1����Ц��1������ѩ1�������2

(1. �������ӿƼ���ѧ ����ѧԺ���������뵼������������������ص�ʵ���ң����� ������710071��

2. ����ͨ��ѧԺ ������������ ������710106)

ժ Ҫ��

ժ Ҫ�����һ���ڲ�����4λ�������Ķ�������λsigma-delta��������Ϊ���������·�ж�λDACԪ��ʧ�䵼�µ��ź�г��ʧ�����⣬��sigma-delta����������CLA(Clocked averaging algorithm)������߶�λDAC�����Զȣ�ͬʱ���ö�̬Ƶ�ʲ����������ӻ��������ȶ��ԡ��������ź�Ƶ�ʴ���Ϊ24 kHz����������(OSR)Ϊ128�����óߴ�Ϊ0.5 ?m��CMOS���գ�������ѹΪ5 V�����Խ���������������ź�Ƶ��Ϊ20 kHzʱ�������(SNR)��103 dB������������ź����Ӳ���̬��ΧΪ102 dB����������������Ϊ87 mW��оƬ�����Ϊ2.56 mm2��

�ؼ��ʣ�

sigma-delta�����������ص��ݻ��������߾�������λ��

��ͼ����ţ�TN432 ���ױ�־�룺A ���±�ţ�1672-7207(2010)02-0592-08

Design of high-resolution audio multibit sigma-delta modulator

SHI Li-chun1, 2, YANG Yin-tang1, LI Di1, WU Xiao-feng1, DING Rui-xue1, LIANG Hong-jun2

(1. Key Laboratory of Wide Band-Gap Semiconductor Materials and Devices, Ministry of Education,

School of Microelectronics, Xidian University, Xi��an 710071, China;

2. Base Department, Xi��an Communication Institute, Xi��an, 710106, China)

Abstract: A two-level single-loop multi-bit sigma-delta modulator was designed with a 4-bit quantizer inside, and it was used for digital audio applications. The modulator used multibit quantization and the dynamic element matching (DEM) technology was adopted to reduce the nonlinearity introduced by multibit quantizer. The modulator was fabricated in a 0.5 ?m CMOS process and 5 V supply voltage, and the input signal bandwidth was 24 kHz at oversampling rate (OSR) of 128. The results show that when a signal of 20 kHz is input, the modulator can achieve a ratio of signal and noise of 103 dB and SFDR of 102 dB. The whole modulator dissipates 87 mW, and the total area of the die is 2.56 mm2.

Key words: sigma-delta modulator; switched-capacitor integrator; high-resolution; multibit

sigma-delta(����?)ģ��ת����(��sigma-delta ADC)[1-3]���ù������������������μ��������˶�ת������ģ���·�����Ҫ���Ҵ�������ת�������ִ���CMOS�����ر���ݣ���Ϊʵ���е��ٸ߾�ģ��ת��������ѡת��������������Ƶ���������������Ӳ���������ͨѶ������õ��㷺Ӧ�á�sigma- delta ADC�ɦ�?������(SDM)�����ֳ����˲�����ɡ�sigma-delta��������sigma-delta ADC�ĺ��IJ��֣���ṹѡ��͵�·������ƾ���������ת�����IJ������ʺ�ת�����ȵ���Ҫ����ָ�ꡣ1λ�Ͷ�λ��?������(�ֱ�ָ���������Ȼ�ֱ���Ϊ1λ�Ͷ�λ�Ħ�?������)��������Ƶ����߾���ת���㷺���õ�2�ַ�����1λ��?������[4-6]���ڲ���1λ�����������й��е�����������������Ȼ�����ڸ����������ʵ�����£�1λ����������ʽ������(Pattern or idle tones)����ֱ���Ҳ���ޡ���ˣ�Ϊ�õ��߷ֱ����Լ���Сʽ��������1λ������ͨ�����ø߽ṹ��Ȼ�����߽�1λ��������������������Ҫ���и�ѹ���ʲ��ܿ����ȶ����˷ţ�����µ�·�Գĵ������ͻ���ѹ�İڶ��������С���λ��?������[7-9]���������ŵ㣺(1) ����λ��ÿ����1λ��������ת���������6 dB��(2) ��λ�������еĻ��ֲ���С��ʹ���˷Ŷ��ʺʹ�����Ҫ���1λ���������˷ŵ�Ҫ��ϵͣ�(3) ��λ���������ж�������ȼ�ʹ�ÿ�������ϴ���źŷ��ȣ�ͬʱ��������������������������Ա�С����ˣ���������ʽ������ҲС������λ������Ҳ�������±ˣ�������·�ж�λDACԪ��ʧ��ᵼ���źŵ�г��ʧ�档Ϊ�˽��������⣬��λ������������ö�̬Ԫ��ƥ�似��[10-12]���������������1���ڲ�����4λ�������Ķ�����sigma-delta��������ͬʱ����CLA(Clocked averaging algorithm)������߶�λDAC�����Զȡ�Ϊ����ǿ���������ȶ��ԣ��������˶�̬Ƶ�ʲ���������ģ��������������źŴ���Ϊ24 kHz���ڹ���ʱ��Ϊ6.144 MHz����������Ϊ128ʱ�������������(SNR)Ϊ103 dB������������ź����Ӳ���̬��ΧΪ102 dB�����Ĵӵ�����ϵͳ�ṹ��ѡȡ������·ģ�������Լ����Խ���Ƚ��н��ܺ� ���ۡ�

1 sigma-delta�������ṹ

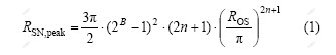

1����������ΪROS���ڲ�������ΪBλ��n���������������ȿɱ�ʾΪ[1-2]��

���У�RSN, peakΪ��ֵ����ȣ�ROSΪ�������ʡ�

���ڵ����߽����������ȶ������⣬�༶�߽�����(MASH)�ṹ���е�·���Ӽ�����й©ȱ�㡣�������߲����ܹ������ȶ��Ķ������ṹ�����������Լ��ٵ���������ģ���������Ӷ���СоƬ������ġ����ڵ�����������Ƶ�źţ��źŴ���С������ѡ���Ĺ�������(128)���������������IJ���Ƶ��Ϊ6.144 MHz��Ϊʵ�����Ŀ�꣬�ڲ�������λ��ȷ��Ϊ4����ʱ����ʽ(1)��֪�������ȿɴ�118 dB����Ҳ����·��������������һ����������

�������ṹ��ͼ1��ʾ���ڴ�ͳ�ṹ������1�����ź�����˵���2�������������ǰ��ͨ·(��ͼ1��������ʾ)���Ӷ���С��1����������������ȣ���һ�������˵�1���������зŴ������ʺʹ�����Ҫ��������ʹ�Ŵ����������һ�������ɴ˼�С�������ص��ݣ���ߵ�����������ȡ�ͼ1����������4λ�����������ڷ�����λDAC�е�������������ʧ�����������ԣ��Ӷ��ή�͵����������ܣ����ԣ�����в���һ�ֶ�̬Ԫ��ƥ��(Dynamic element matching��DEM)������CLA�������Խ������ַ��������ص�Ӱ�졣

2 �������ĵ�·ʵ��

2.1 ��������·�ṹ

��������·���ÿ��ص���(Switched-capacitor, SC) ��������ȫ��ֵ�·��ʵ�֣��Ӷ����Լ�Сʱ����ͨ��ż��г�����ĵ͵�Դ�����ȵ�·���������ص�Ӱ�졣ͼ2��ʾΪ2�צ�?�������ĵ�·ͼ������2�����ص��ݻ�������1��4λADC��1����̬Ԫ��ƥ��(DEM)ģ���Լ�2���ɿ��ص�������ʵ�ֵĶ�λDAC��

16-level flash ADC��ʾ16����λ����ģ����ת������16-level ADC��ʾ16����λģ��ת������X(z)Ϊ�����źŵ�z����ʽ

ͼ1 ��?�������Ľṹ

Fig.1 High-level sigma-delta modulator topology

ͼ2 �������Ŀ��ص��ݵ�·

Fig.2 Switched-capacitor circuit of modulator

�ɿ��ص��ݹ��ɵ�ȫ���ʽ���������亯��ȡ���ڿ��ص�����������ֵ���뿪�ص�������ľ���ֵ�ء����ǣ�����ʵ�ʿ��ش��ڵ�ͨ���裬SC������������뿪��������(kT/C����)��������ݹ�С��ʹ�ÿ���������������������ö࣬�Ӷ���Ϊ��������ϵͳ����ȵ���Ҫ���ء������ǵ�1��������֮�еIJ�����·���������������ֱ�ӵ����������ź��ϡ���ˣ�����ȷ���������IJ������ݣ�ʹ�俪����������Ӱ������������ܡ�����Cs��ϵͳ�������� RSN, max�Լ���������ROS֮��Ĺ�ϵ[13]Ϊ��

![]()

ʽ�У�VpeakΪ�����źŵĵ�λ��ֵ��kΪ��������������TΪ����ѧ�¶ȡ�Ϊ��ʹ��1�����������������Լ�����DAC�е����������������������Ӱ����������ȣ��������㣬��1���������IJ�������ȡΪ4.8 pF��DAC��������Ϊ4 pF�����ڵ�������·���������ι��ܣ���2���������IJ��������õ����ƣ���ϵͳ����ȵ�Ӱ�����С�����ԣ���2�����������������Լ�����DAC�е������п���ȡСЩ��ȡ��1�����ֵ�·�е��ݵ�1/4������Ҫ��

������������ѹΪ5 V��Ϊ����������������̬��Χ�����������������ģ��ƽ���Ϊ��ͬ�����ڻ���ѹ��Ϊ2.4 V���������Ĺ���Ƶ��Ϊ6.144 MHz����Ƭ���ṩ6.144 MHzʱ���ź�CLK������Ƭ��2�����ʱ�Ӳ�����·(ͼ3)������2������ص���ʱ���ź�f1��f2���Լ�f1��f2���ӳ��ź�f1d��f2d�������ƻ������IJ����ͻ��֡�f1d��f2d�����������˲������ص�ʱ����ͨ���źŵ�Ӱ�졣

2.2 ģ���·���

2.2.1 �������

���ص�·�ṹ��ͼ4��ʾ�����ô����Ż��ߵ���MOS��ʵ�֡�Ϊ�˼��ٲ����ź����������ţ��������ݲ����¼��������ͼ2����f1d��f2d���ƵĿ���һ�����ӵ��ݵ��¼��壬��һ��ֱ�����źŻ����������������Щ���ص���������ֱ�ӶԻ��������ܲ����ϴ��Ӱ�죬��ˣ���Щ���ز��ô�����ʵ�֡������ſ��ص�ͨʱ����ܹ���������������Ч��ͨ����ΪNMOS��PMOS�ܵ�ͨ����IJ������ȵ���MOS�ܿ��ص�ͨ����С���Ӷ��ɼ�С������������Ӱ�졣�������ضԵ���������Ӱ��С�����õ���PMOS��NMOS��ʵ�֡�����ϵͳ��Դ��ѹΪ5 V����ˣ�����Ҫʱ�ӵ�ѹ���ߵ�·����ʱ�Ӳ�����·������ʱ��ֱ������������NMOS��PMOS�ܡ�

2.2.2 �Ŵ������

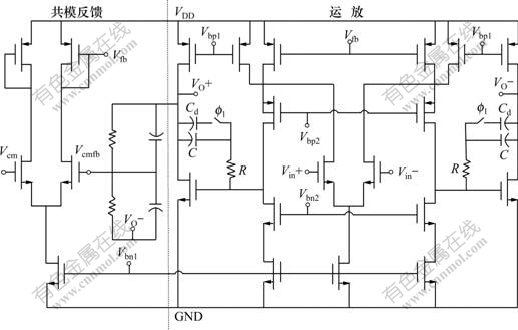

�������Ǧ�?����������Ҫģ�飬���ص��ݻ��������ھ��ȸߣ������������Ĺ�����ʵ�֣���ˣ���Ϊ��Ƹ߾���ת��������ѡ�����������ص��ݻ������ĺ���������Ŵ�������1��������������ȫ��ֽṹ��A��Ŵ�����·��ͼ5��ʾ�����ô�����ʱ�乲ģ�������۵�ʽ��Դ��դ�ṹ����������Ͳ������ṹ�Լ���ģ���������������Ч�����������ģ��ƽ�ı仯���Ӷ�ʹ��·���и�ǿ���ȶ��ԡ�

ͼ3 ʱ�ӷ���

Fig.3 Clock scheme

(a) ���ܿ��أ�(b) ��������

ͼ4 ���ص�·�ṹ

Fig.4 Circuit structure of switches

VDDΪ��Դ��ѹ��VcmΪ�����ģ��ƽ��VcmfbΪ���������ģ��ƽ��Vin+��Vin-Ϊ��������źŵ�ѹ��

VO+��VO-Ϊ�������źŵ�ѹ��Vbp1, Vbp2, Vbp3��Vbp4Ϊƫ�õ�ѹ��GNDΪ��Դ��

ͼ5 �Ŵ�����·

Fig.5 Amplifier schematic

�Ŵ��������ܲ���ָ����Ҫ��������ֱ�����桢��λ���������ѹ�����Լ�����ڷ������У�����ֱ������͵�λ���������ҪӰ����������������ͼ�����ѹ���ʾ����������Ľ����ٶȣ�����ڷ�������������������Χ��Ϊ���������롢����ڷ���ʹ���롢�����ģ��ƽͬΪ2.4 V(�ӽ�1/2��Դ��ѹ��2.5 V)���������ѹ��ȣ�����Ҳ�ɼ�������ơ��Ŵ�������RCƵ�ʲ��������ڲ�������C�ϲ���1�����ص���Cd���ж�̬�������ڲ�����ʱ���˷Ź����ӽ�ȫ������״̬�����ص���Cd���룬ʹ���˷ŵ���λԣ�������ȶ������ӣ��ڻ�����ʱ�������ص���Cd�Ͽ��������˷ŵĵ�λ��������Ͱ��ʣ��Լ�С����������й¶���������ʱ�䡣�Ŵ������������1��ʾ�����У��˷���������Ե������������ܵ�Ӱ����Ժ��ԡ���2���������зŴ����Ľṹ���1���е���ͬ�������为�ص��ݱȵ�1���������зŴ������ص���С�����������������һ�����������Σ����ԣ���2���˷�����Ҫ��ȵ�1�����˷������Ե͡�

��1 �Ŵ������ܲ���

Table 1 Amplifier performances

2.2.3 ��������ʵ��

��λ��?��������������ͨ����1������ADC��4λ�������ĵ�·�ṹ��ͼ6��ʾ������Mid-Tread������ʽ��1/2���̶ȵ�ѹͨ�������ѹ����8�����IJο���ѹ�ȼ���ͨ�����ص��ݷ������Բ���8�����IJο���ѹ�ȼ�������ź�ͨ�����ص��ݲ���ʵ����ο���ѹ�����Ȼ�������ֱȽ������бȽϣ��ȽϽ������16�ȼ��¶ȼ��롣�¶ȼ��뾭������ת��Ϊ5��4λ��������������������⡣

��������Ƶ��ص��DZȽ������Ƚ���ʧ����ѹ��ᵼ������������������ݴ������ִ��������������䷴����࣬�Ӷ�ʹ�����������ѹ����ȫ�ȶ���Ϊ�˼�С�Ƚ���������ʧ����ѹ������Ԥ�Ŵ�����Ƚ���[14-16]��Ԥ�Ŵ�ͬʱҲ��С���������Ի����������Ӱ�졣�Ƚ�����·�ṹ��ͼ7��ʾ���ýṹ����1����������Ԥ�Ŵ�Ŵ�����2�������Ժ�1��RS���������ڱ����࣬Ԥ�Ŵ�������������������ȶ��㣬ͬʱ��PMOS������Ҳ������Ϊ��Դ��ѹVDD���������࣬2�������Դ���1���������������������

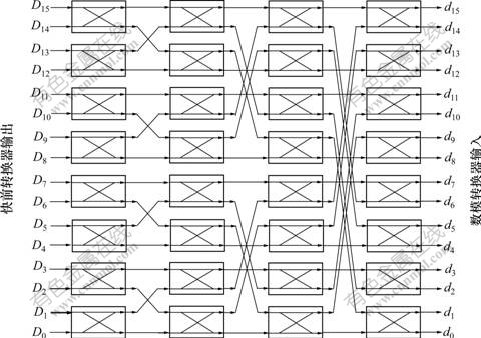

2.2.4 DEMģ�����

��λ����������Ҫ��ȱ���ǶԷ���DAC�ķ�����������С�DAC�����������Ҫ��Դ���ڲ��������м��ʧ�䡣�����ַ�������������������ֱ�ӵ����������ź�֮�ϵģ�����������������ȵ�Ӱ��ʮ�����ԣ����ԣ�������ö�̬Ԫ��ƥ��(DEM)������������DAC�ķ����������IJ���CLA����[12]��������·�����ң���С��������ʵ��CLA��DEMģ����ͼ8��ʾ��������������¶ȼ���ķ���·����DEM���Һ�������DAC��DEM��ÿһ����ģ����������1���źż�Ĺ�ϵȷ������·������2���źŲ�ͬʱ��ı䴫��·���������ģ������ź�������ϣ�������һ��ģ������ظ�������������4��·����ѡ��ʹ�¶ȼ����ź�α�������DAC���Ӷ�ʹ��DAC�ĵ�·���ɹ̶�ʧ������ķ�������CLAת��Ϊһ���������������������ֲ����źŴ��ڵ�����������С���ɴ˶Ե�����������Ӱ�������

(a) ��������·�ṹ��(b) ��ԪADC�ṹ

VFSΪ������������ѹ��V+��V-Ϊ�������������źţ�D0��Ϊ1λADC��������DoutΪ�Ƚ���������

ͼ6 4λ�������ĵ�·�ṹ

Fig.6 Circuit structure of 4-bit quantizer

ͼ7 Ԥ�Ŵ������Ƚ���

Fig.7 Latch comparator with preamp

ͼ8 ����CLA������DEMģ��

Fig.8 DEM module with CLA

(a) DAC��·��(b) DAC��Ԫ�ڲ��ṹ

VrefΪDAC�ο���ѹ��diΪDAC��Ԫ���룻A+��A-ΪDAC��Ԫ���

ͼ9 DAC��·

Fig.9 DAC circuit topology

2.2.5 ����DAC���

2��DAC�����ÿ��ص���ʵ�֡�2��DAC�ṹ��ͼ9��ʾ�����Ƕ���16����ͬ��DAC��Ԫ��ɡ�2��DAC������DAC��Ԫ�е��ݵ�Ԫ��ͬ�⣬�ṹ��ȫ��ͬ���ڲ����࣬DAC��Ԫ��2�����ݸ��Գ�����ΪC��Vref��-C��Vref(���У�CΪ���ݣ�VrefΪ�ο���ѹ)����������ݷ����źž���2�����������������һ���������������ͬһ���������������16��CDCA���ݾ���ɴ������ʵ�ַ��������źŵ�ģ���ѹ��ת����ͬʱ�������ź��������ɻ��ֹ��̡�

3 ���ɵ�·��ͼ���

���ɵ�·��ͼ��ƶ�ʵ�ּ��ɵ�·������������Ҫ�ģ��������ŵ�·������ģ�⼯�ɵ�·��Ƶijɰܡ��������߶Ե�������ͼ������ƣ�Ϊ�˱�֤��ַŴ�����ȷƥ�䣬���öԳƺ�ƽ�⼼�����а�ͼ��ƣ��ر��������ֶԻ�ʹ�÷ְ뽻���Դﵽ�ߵ�ƥ�侫�ȡ�Ϊ�˼�����Դ�Ե�·�ĸ��ţ��������ڲ�����2·��Դ�߹��磺һ·�������������źŵ�DEM��Ԫ��2�����ʱ�Ӳ�����·����һ·����2��������������2���ֵ�·�����ϸ���롣�Ƚ�������źŸߡ��͵�ƽ�Ŀ���ת������Ի������������ţ���ˣ��ԱȽ����ͻ�������Ҳ���и��롣Ϊ��ȥ����Դ�����ĸ��ţ��ڵ�Դ��֮�仹����һЩMOS���ݡ�

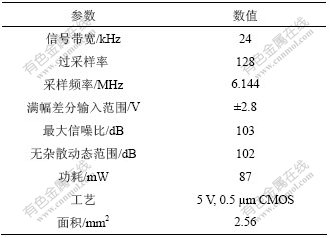

4 �������

����Ʋ���0.5 ?m CMOS����ʵ�֣�����оƬ������������·�����������Ϊ2.56 mm2����5 V������ѹ�£�����Ϊ87 mW���ڹ�����Ƶ��Ϊ6.144 MHz����������Ϊ128ʱ�����������������Ϊ-1 dB��Ƶ��Ϊ20 kHz�IJ�������źţ��������������������вɼ�������MATLAB�в���16 384����ٸ���Ҷ�任(FFT)��������õ������������Ϊ103 dB������ź�����ɢ��̬��ΧΪ102 dB����Ч����ԼΪ17λ��������оƬ��Ҫ���ܲ������2��ʾ�������о���������������ĶԱ����3��ʾ���ɼ����������ֱ��ʾ��ȴﵽ���ߵ�����ȣ���ͬ�ߴ�Ϊ0.5 ?m��CMOS����[5]��ȹ���Ҳ�������͡�

��2 ������оƬ����

Table 2 Performance and specification of modulator

��3 sigma-delta���������ܵĶԱ�

Table 3 Performances of some sigma-delta modulators

5 ����

(1) �����1���߾��ȶ�λ��?(sigma-delta)���������õ���������4λ��������ߵ������ľ��ȣ�����CLA�������Ӷ�λDAC�����Զȣ�ʹ�ö�̬Ƶ�ʲ���������ǿ���������ȶ��ԡ�

(2) ��������0.5 ��m CMOS����ʵ�֣�оƬ�����Ϊ2.56 mm2����5 V��Դ��ѹ�¹������������źŴ���Ϊ24 kHz��������Ƶ��Ϊ6.144 MHz����������Ϊ128ʱ���������������(SNR)�ɴ�103 dB������Ϊ87 mW��

(3) �õ����������ֳ�ȡ�˲����ɹ��ɸ߾��Ȧ�?ģ��ת������Ӧ����������Ƶ����

�ο����ף�

[1] Candy J C, Temes G C. Oversampling delta-sigma data converters theory, design and simulation[M]. New Jercy: IEEE Press, 1992.

[2] Schreier R, Temes G C. Understanding delta-sigma data converters[M]. New Jercy: IEEE Press, 2005.

[3] Schreier R. An empirical study of higher-order single-bit delta-sigma modulators[J]. IEEE Trans Circuits Syst II, 1993, 40(8): 461-466.

[4] Zierhofer C M. Adaptive sigma-delta modulation with one-bit quan-tization[J]. IEEE Trans on Circuits and Sys II, 2000, 47(5): 408-415.

[5] CHEN Lei, ZHAO Yuan-fu, GAO De-yuan, et al. A 16-bit stere audio ��? A/D Converter[J]. Chinese Journal of Semiconductors, 2006, 27(7): 1183-1188.

[6] Geerts Y, Steyaert M, Sansen W. Design of multi-bit delta-sigma A/D converters[M]. Boston: Kluwer Academic Press, 2002.

[7] LU X. J. A novel signal-predicting multibit delta-sigma modulator[C]//Proc of the IEEE Int Conf on Electronics, Circuits and Sys. Tel-Aviv, Israel, 2004: 105-108.

[8] Leung B H, Sutarja S. Multi-bit sigma-delta A/D converters incorporating a novel class of dynamic element matching techniques[J]. IEEE Trans Circuits Syst II, 1992, 39 (1): 35-51.

[9] Chen F, Leung B H. A high resolution multibit sigma-delta modulator with individual level averaging[J]. IEEE Journals of Solid State Circuits, 1995, 30(4): 453-460.

[10] Yasuda A, Tanimoto H, Lida T. A third-order ?-�� modulator using second-order noise-shaping dynamic-element matching[J]. IEEE Journals of Solid State Circuits, 1998, 33(12): 1879-1886.

[11] Brooks T L, Robertson D H, Kelly DF, et al. A cascaded sigma-delta pipeline A/D converter with 1.25 MHz signal bandwidth and 89 dB SNR[J]. IEEE Journals of Solid State Circuits, 1997, 32(12): 1896-1906.

[12] Kwan T, Adams R, Libert R. A stereo multibit ��? DAC with asynchronous master-clock interface[J]. IEEE Journals of Solid State Circuits, 1996, 31(12): 1881-1887.

[13] Hauser M W, Broderson R W. Circuit and technology considerations for MOS delta-sigma A/D converters[C]//Proc IEEE International Symposium on Circuits and Systems. San Jose, USA, 1986: 1310-1315.

[14] ��Ц��, ������, ʯ����, ��. �����ٵ���CMOS��̬�Ƚ��������Է���[J]. ���ϴ�ѧѧ��: ��Ȼ��ѧ��, 2009, 40(5): 1354-1359.

WU Xiao-feng, LIU Hong-xia, SHI Li-chun, et al. Characteristic analysis of an high speed low power CMOS dynamic comparator[J]. Journal of Central South University: Science and Technology, 2009, 40(5): 1354-1359.

[15] �½���, �ο���, ����, ��. һ������GSM��80 dB��̬��Χ��-?������[J]. �뵼��ѧ��, 2007, 28(2): 294-301.

CHEN Jian-qiu, REN Jun-yan, XU Jun, et al. An 80 dB dynamic range ��-�� modulator for a GSM system[J]. Chinese Journal of Semiconductors, 2007, 28(2): 294-301.

[16] CAO Ying, REN Teng-long, HONG Zhi-liang. A 16 bit 96 kHz Chopper-Stabilized sigma-delta ADC[J]. Chinese Journal of Semiconductors, 2007, 28(8): 1204-1210.

�ո����ڣ�2009-09-12�������ڣ�2009-12-01

������Ŀ�����ҽܳ��������������Ŀ(60725415)�����Ҹ����о���չ�ƻ�(��863���ƻ�)��Ŀ(2009AA01Z258��2009AA01Z260)

ͨ�����ߣ�ʯ����(1976-)���У�ɽ����ƽ�ˣ���ʿ�о�������ʦ�����¸߾���ģ��ת��������о����绰��13629291250��E-mail: lc-shi@126.com