�߾���S-DADC�е����ֳ�ȡ�˲������

��Ц��1��������2�����2�����˸�1��ʯ����2

(1. ���ϿƼ���ѧ ��Ϣ���������ѧԺ������ ��̶��411201��

2. �������ӿƼ���ѧ ����ѧԺ �������뵼������������������ص�ʵ���ң����� ������710071)

ժ Ҫ��

ժ Ҫ�����1��Ӧ���ڸ߾���sigma-deltaģ��ת����(S-DADC)�����ֳ�ȡ�˲��������ֳ�ȡ�˲�������0.35 mm����ʵ�֣�������ѹΪ5 V�����˲������ö༶�ṹ���ɼ�����״�˲����������˲�����խ���������Ӧ����˲�����ɡ�ͨ���Ը����˲����Ľṹ�������Լ�ϵ�������Ż���ƣ���Ч����С�˵�·������������˲����Ĺ��ġ�����Ƶ����ֳ�ȡ�˲���ͨ��Ƶ��Ϊ21.77 kHz��ͨ������ϵ��Ϊ��0.01 dB���������˥��120 dB���о�������������˲�����128��������������S-D������������������д������õ�������ʧ��ȴ�102.8 dB�����ֳ�ȡ�˲������Ľ�Ϊ49 mW�����ԼΪ0.6 mm��1.9 mm���ﵽ�˸߾���ģ��ת������Ҫ��

�ؼ��ʣ�

S-DADCģ��ת���������������������������˲�����

��ͼ����ţ�TN432 ���ױ�־�룺A ���±�ţ�1672-7207(2010)03-1037-05

Design of digital decimation filter for high resolution S-DADC

WU Xiao-feng1, LIU Hong-xia2, LI Di2, HU Shi-gang1, SHI Li-chun2

(1. School of Information and Electrical Engineering, Hunan University of Science and Technology,

Xiangtan 411201, China;

2. Key Laboratory for Wide Band-Gap Semiconductor Materials and Devices of Ministry of Education,

School of Microelectronics, Xidian University, Xi��an 710071, China)

Abstract: A multistage digital decimation filter for high resolution sigma-delta analog-to-digital converter (S-DADC) was designed. The filter was fabricated by a 0.35 mm process and operates at a voltage of 5 V. The filter consists of a cascade-integrator-comb (CIC) filter, a compensation filter and narrow transition-band finite impulse response (FIR) half-band filter. Due to the optimal design of the architecture and order and coefficient of filters at various levels, the decimation filter effectively reduces the circuit area and power dissipation. The decimation filter has pass band of 21.77 kHz, pass band ripple coefficient of ��0.01 dB and stopped band attenuation of 120 dB. Experimental results show that by processing the bit stream from a 2-order ��-�� modulator with an oversampling ratio of 128, a signal-to-noise-distortion ratio (SNDR) of 102.8 dB is obtained for the filter. The filter has a good performance and its dissipation powder is only 49 mW. The occupied die area is about 0.6 mm��1.9 mm. The filter well meets the demand of high resolution S-DADC.

Key words: S-DADC analog-to-digital converter; modulator; decimation; digital filter

S-DADC���ѳ�Ϊ�߾���ADC[1]��Ƶ�һ����ʵ���еĽ��������S-DADC��S-D�������ͳ�ȡ�˲�����ɣ�S-DADC�е������Ļ���ԭ���ǹ��������������Ρ���S-DADC�У���Ҫ�������ֳ�ȡ�˲����Ե�������������ݽ��г�ȡ����ԭ���Ĺ�����Ƶ�ʽ��͵��ο�˹�ز����ʣ���ͬʱ��ģ���ź�ת���������źš����ֳ�ȡ�˲�������Ҫ�������Ƴ��������������Ͳ���Ƶ�ʺͿ���������ĵ���ҪĿ�������1��Ӧ����18λ����S-DDC�е����ֳ�ȡ�˲��������ֳ�ȡ�˲��������ܲ������£������źŲ���Ƶ��Ϊ6.144 MHz������źŲ���Ƶ��Ϊ�ο�˹���ʼ�48 kHz����������Ϊ128��ͨ��Ƶ��Ϊ21.77 kHz���������Ƶ��Ϊ26.23 kHz��ͨ������ϵ��Ϊ��0.01 dB���������˥��120 dB���������ֳ�ȡ�˲���������S-DADC����������зdz���Ҫ��Ӱ��[2-4]���ڴˣ��������߲��ö༶�ṹ[5-7]��ʵ����ʽ�����Ը����˲�����������Ľ������̶��Ż���

1 ����ṹ

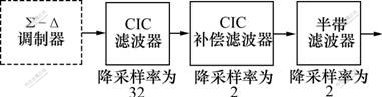

�༶�ṹ���Լ���ؼ�С�˲����Ľ�������ˣ����IJ��ö༶�ṹ(��ͼ1)���ﵽ��������Ŀ�ġ�����У�ͬʱ�������յ����Ŀ�꣬����һЩ������˲�������һ����С������ġ�

ͼ1 ���ֳ�ȡ�˲����ṹ

Fig.1 Structure of digital decimation filter

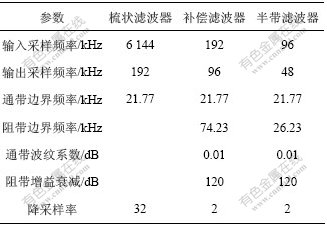

�����S-DADCʱ�����ڵ�1����ȡϵ���Ƚϴ�ͨ��ֻռ�������Ƶ�ʵĺ�С���֣���ˣ���1���˲������Բ���1��������˲�����������״(Cascade of integrators comb, CIC)�˲���[8]�������Դ���С��1���˲����Ľ�����Ҳʹ��������Ƽܶࡣ��Ȼ��1����״�˲����������С������״�˲�����ͨ������˥���������Ҫ�ڵ�2����������˥������ˣ���2������CIC�����˲�����CIC�����˲���ʵ������1��FIR�˲������併������Ϊ2����3�����ð���˲���������˲�����һ��ϵ��Ϊ0������һ��ϵ���Գƣ���ͽ����˵�3���˲�����������3���˲�����������Ϊ2��ͨ���������Եõ������˲����������������Ƶ�ʡ�ͨ��������߽�Ƶ�ʼ��������ʣ����1��ʾ��

��1 �����˲�����ָ��

Table 1 Performance of filters at various levels

2 ���ֳ�ȡ�˲������

2.1 ��״�˲��������

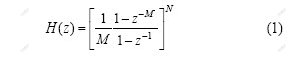

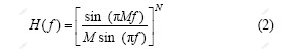

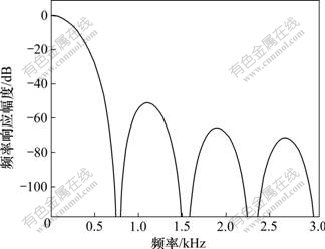

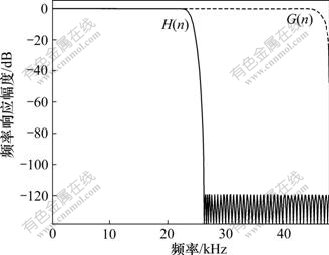

��״�˲�����һ���ڸ��ٳ�ȡ���ֵϵͳ�зdz���Ч�ĵ�Ԫ����Ҫ��������ͨ�ź�S-DADC�С����ö༶������״�˲����Ľṹ���Ż���1���˲�����Ƶ����Ӧ��CIC�˲����Ĵ��ݺ���Ϊ��

��Ƶ����ӦΪ��

���У�MΪ��״�˲����Ľ������ʣ�NΪ��״�˲��������ĸ���������Ƶ����Ӧ��ͼ2��ʾ(��M=8Ϊ��)��һ����˵���ڶ�L�ס���������ΪM��S-Dģ����������н�Ƶʱ����״�˲����ļ�������Ҫ�ﵽL+1���ϣ����ܲ����㹻������˥��[9]����ͼ2��֪����״�˲�����ͨ���ڻ�˥������ˣ���2���˲����ò����˲�����ʵ�֡��趨��״�˲��������Ƶ��Ϊ�ο�˹�ز����ʵ�4������ԭ���ǣ����������Ƶ��̫�ߣ����������˲����Ľ�������������������ģ����������Ƶ��̫�ͣ����൱����������״�˲��������ġ�����������ͨ���߽粻�䣬�����ԣ�ͨ��Ƶ��Fp����˥��������ͬʱ��Ҳʹ��ͨ���߽硰����������߽磬����ͨ����������

ͼ2 ������״�˲�����Ƶ����Ӧ(M=8, N=4)

Fig.2 Frequency response of CIC filter (M=8, N=4)

�������������ȷ�����ĵļ�����״�˲����ĽṹΪ����������N=5����������M=32��

2.2 CIC�����˲��������

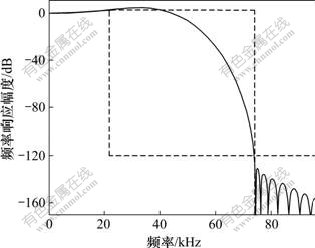

Ϊ�˲���CIC�˲�����ͨ����˥������2������CIC�����˲�����CIC�����˲�����1��FIR�˲� ������Ʋ����˲�����Ҫ����FIR�˲�������Ʒ���������ơ����IJ����б�ѩ����ѱƽ��������CIC�����˲����������ֽṹ�������ʱ��һ���Dzο�Mcclallan��Remez�㷨���е���������˲�����ϵ ��[10]�����Ե���Matlab�е�Remez��������ƣ�Ҳ�ɵ���Matlab8.0 filter design toolbox�е�CIC�����˲���ģ�������[11]��CIC�����˲���Ƶ����Ӧ��ͼ3��ʾ����ͼ3�ɼ��������˲�����ͨ������������һ���IJ������ã�����Ҫ��CIC�˲��������������յIJ��������

ͼ3 CIC�����˲�����Ƶ����Ӧ

Fig.3 Frequency response of CIC compensation filter

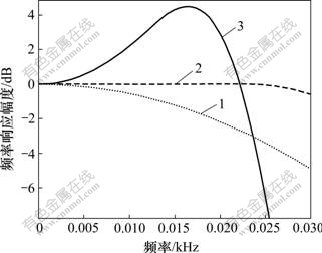

���ݱ�1�е�CIC�˲�����Ʋ�������������Ϊ32������ʱ(Ӳ�����ʱ�ķ�����ʱ)Ϊ1���ݲ����˲����ı߽�Ƶ�ʺͽ��������������صIJ����˲��������Եõ���Ӧ�IJ����˲���������CIC�˲����Լ�������(Cascade filter)�Ժ��Ƶ����Ӧ��ͼ4��ʾ����ͼ4��ʾCIC�˲�����CIC�����˲����ļ��������������õIJ����˲������Ժܺõز���CIC filter��ͨ���ڵ�˥�����ܴﵽ��Ƶ�Ŀ�ꡣ

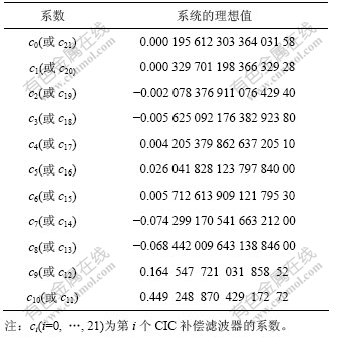

��Matlab����õ�CIC�����˲�����������22�ף�����ϵ������2���ӱ�2���Կ�����CIC�����˲�����ϵ���ǶԳƵģ�����22��ϵ���У�ֻ��11�����ظ���ϵ������Ӳ��ʵ��ʱ������ص����ʹ�����˲����������Сһ�롣

1��CIC�˲�����2��Cascade�˲�����3��CIC�����˲���

ͼ4 CIC�˲�����CIC�����˲�����Cascade�˲�����

Ƶ����Ӧ

Fig.4 Frequency response of CIC filter, CIC compensation filter and Cascade filter

��2 CIC�����˲�����ϵ��

Table 2 Coefficient of CIC compensation filter

2.3 ����˲��������

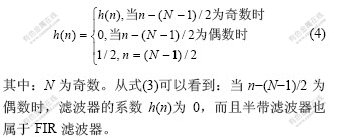

��������һ���˲���ʱ������ֻ��Ҫ2�����������˲������ɣ�������˲���������������Ҫ�����Ľ�һ��ϵ��Ϊ0����ˣ�������ܴﵽͬ��Ч������ͨFIR�˲�����˵������˲����˷���Ԫ����һ�롣��ˣ����һ���˲������ð���˲���[12]������˲�����Ƶ����ӦΪ��

![]()

�����˲��ĵ�λ������ӦΪ��

FIR�˲����ĵ�λ������Ӧ�жԳ���[13]����ˣ�����˲����ֻ��N/4+1�����ظ�ϵ�����벹���˲���һ��������˲���Ҳ����FIR�˲��������ǵ�����˲������ص㣬�����б�ѩ��ƽ�����ư���˲���ʱ�����Լ���ơ��ٶ���Ҫ���1������ΪN�İ���˲�������(N-1)/2Ϊ����ʱ(��Ϊż������h(0)=h(n)=0���൱��1��N-2�İ���˲���)����Ƶ�ͨ���߽硢����߽�Ͳ���ϵ���ֱ�Ϊ��p����c�ͦ�p�������õȲ������1��(N-1)/2����ͨFIR�˲���g(n)����ͨ������ϵ��Ϊ2��p��ͨ���߽�ϵ��Ϊ2��p������2��c���У��ʿ��Խ����g(n)������߽�ϵ����Ϊ�С����壺

![]() (5)

(5)

����

(6)

(6)

���У�n=0, 1, ��, N-1������G(n)�IJ������g(n)��Ȼ���ݹ�ʽ(6)�õ�h(n)��ϵ�������ǵ�Ƶ����Ӧ��ͼ5��ʾ��

����Matlab8.0/simulink/filter design toolbox�е�Halfband�˲���ģ����Ƹ����㡣���յõ���159��Halfband�˲�����ϵ������Ч��Ϊ40����

ͼ5 G(n)��H(n)��Ƶ����Ӧ

Fig.5 Frequency response of G(n) and H(n)

3 оƬ���Խ��

����оƬ����Chartered 0.35 mm CMOS����ʵ�֣�������ѹΪ5 V��

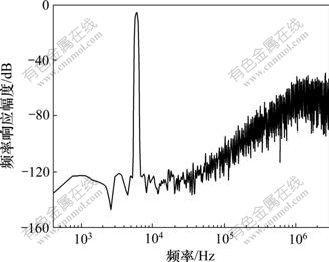

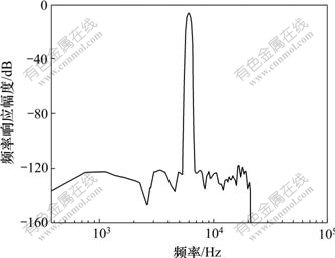

ģ����������ֺ����ֽ������˲�������ʹ�ø��뻷���и��룬��ֹ���ֲ��ֵ�����Ӱ��ģ���·���֡�CIC�����˲����Ͱ���˲�����ϵ������CSD (Canonic signed digit)��ʵ�֣���ʵ���˲���ϵ�����̶ȵ��Ż�����·ʹ����λ���ͼӷ���ʵ�֡�ʹ���������Ƕ�ģ�������������Զ˿ڵ��źŽ������ݲɼ�����ʹ��MATLAB��������Ƶ�������ɵõ��������Ƶ��ͼ��ͼ6��ʾ����ͼ6�ɼ����������ź�Ϊ-4 dB(Ƶ��Ϊ6 kHz)ʱ���ڴ���24 kHz�ڣ�����ʧ��� (SNDR)Ϊ102.8 dB����Чλ��Ϊ16.79λ��ʹ����ͬ�ķ����������������˲��������ź�Ƶ����ͼ7��ʾ����ͼ7�ɼ�������Ƶ����ֽ������˲���ͨ����ֹƵ��Ϊ21.77 kHz�����ɴ�Ϊ4.5 kHz��ͨ������ϵ��Ϊ��0.01 dB���������˥��120 dB����оƬ�IJ��Խ����������������ѹ5 Vʱ������Ƶij�ȡ�˲������ֹ��Ľ�Ϊ49 mW�����ԼΪ0.6 mm��1.9 mm��

ͼ6 �������IJ���Ƶ��ͼ

Fig.6 Testing frequency spectrum of modulator

�����ź�Ϊ-4 dB��Ƶ��Ϊ6 kHz������ʧ���Ϊ102.8 dB����Чλ��Ϊ16.79λ

ͼ7 �����˲������Ƶ��ͼ

Fig.7 Output frequency spectrum of digital decimation filter

4 ����

(1) ����Chartered 0.35 ��m CMOS ����ʵ����һ�����ڸ߾��Ȧ�-��ADC�༶������ʽṹ�����ֳ�ȡ�˲����������ֳ�ȡ�˲����Ĵ���Ϊ21.77 kHz���������Ƶ��6.144 MHz����������Ϊ128�����˲�����ϵͳ�ṹ��������ƣ���ȷ�����ö༶�ṹ֮�ֱ�Ը����˲����Ľṹ�������Լ�ϵ�������Ż���ơ�

(2) �������˲��������Ŀ���£����������ŵ�ѡ���Խ�����������ֽ������˲��������Ʒ���Ԥ�ڵ�Ҫ��

�ο����ף�

[1] ����. ���ٸ߾���ģ/��ת��������̬�����[J]. ���Ϲ�ҵ��ѧѧ��: ��Ȼ��ѧ��, 1999, 30(6): 623-625.

LING Yu-hua. A microcomputerizer dynamic railway scale with high-speed and high-glass accuracy A/D conversion[J]. Journal of Central South University of Technology: Natural Science, 1999, 30(6): 623-625.

[2] Hogenauer E B. An economical class of digital filters for decimation and interpolation[J]. IEEE Transactions on Acoustics Speech and Signal Processing, 1981, 29(2): 155-162.

[3] Chen L, Zhao Y F, Gao D Y, et al. A decimation filter design and implementation for oversampled sigma delta APD converters[C]//Proceedings of 2005 IEEE International Workshop on VLSI Design and Video Technology. Suzhou, 2005: 55-58.

[4] Ren S, Siferd R, Blumgold R, et al. Hardware efficient FIR compensation filter for delta sigma modulator analog to digital converters[C]//48th Midwest Symposium on Circuits and Systems. Covington, Kentucky, 2005: 1514-1517.

[5] Brandt B P, Wooley B A. A low-power area efficient digital filter for decimation and interpolation[J]. IEEE Journal of Solid-state Circuits, 1994, 29(6): 679-687.

[6] Goodman J, Carey M J. Nine digital filters for decimation and interpolation[J]. IEEE Trans Acoust, Speech, Signal Processing, 1997, 25(3): 121-126.

[7] Coffey M. Optimizing multistage decimation and interpolation processing[J]. IEEE Signal Process Lett, 2003, 10(4): 107-110.

[8] Aboushady H, Mehrez H. Efficient polyphase decomposition of comb filters in SD analog-to-digital converters[J]. IEEE Trans Circuits Syst ��: Analog and Digital Signal Process, 2001, 48: 898-903.

[9] Candy J C. Decimation for sigma delta modulation[J]. IEEE Trans Comm, 1986, 34(1): 72-76.

[10] Crochiere R E, Rabiner L R. Interpolation and decimation of digital signals: A tutorial review[C]//Proceeding of the IEEE. Houston, 1981, 69: 300-331.

[11] Maulik P C, Chadha M S, Lee W L. A 16-bit 250-KHz delta-sigma modulator and decimation Filter[J]. IEEE Journal of Solid-state Circuits, 2000, 35: 458-467.

[12] Vaidyanathan P P, Nguyen T Q. A ��TRICK�� for the design of FIR half-band filters[J]. IEEE Trans Circuits and Systems, 1987, 34(3): 297-301.

[13] Lu W, Hinamoto T. Design of FIR filters with discrete coefficients via polynomial programming: towards the global solution[C]//IEEE ISCAS. New Orleans, 2007: 2048-2051.

�ո����ڣ�2009-08-10�������ڣ�2009-10-21

������Ŀ��������Ȼ��ѧ����������Ŀ(60206006)�������������������˲żƻ���Ŀ(NCET-05-0851)���������Ƽ����¹����ش���Ŀ�����ʽ�������Ŀ(708083)������Ӧ�ò��ϴ��»���������Ŀ(XA-AM-200701)

ͨ�����ߣ���Ц��(1974-)���У�������Դ�ˣ���ʿ�о�������ʦ�����¸��ٸ߾���ģ��ת��������о����绰��15829738218��E-mail: willow_wxf@hotmail.com