面向FPGA的低功耗多路选择器设计方法

李列文1, 2,桂卫华1,阳春华1,胡小龙1

(1. 中南大学 信息科学与工程学院,湖南 长沙,410075;

2. 长沙师范学院 电子信息工程系,湖南 长沙,410100)

摘要:针对现场可编程门阵列(FPGA)因集成度与速度提高引起的功耗问题,提出一种适合于FPGA的低功耗多路选择器设计方法。该方法基于FPGA中被使用的多路选择器内存在大量闲置晶体管这一现象,采用反向衬底偏置技术对被使用多路选择器中闲置晶体管的泄漏电流进行优化。仿真结果表明:与传统结构多路选择器相比,在保证其他性能的前提下,采用该方法设计的多路选择器泄漏功耗可降低约28.97%。此外,该方法也可应用于FPGA中未被使用多路选择器泄漏电流的优化,可以进一步大幅度降低FPGA的静态功耗。

关键词:低功耗;多路选择器;反向衬底偏置技术;现场可编程门阵列

中图分类号:TN402 文献标志码:A 文章编号:1672-7207(2014)05-1496-07

Design of low-power multiplexers for FPGA

LI Liewen1, 2, GUI Weihua1, YANG Chunhua1, HU Xiaolong1

(1. School of Information Science and Engineering, Central South University, Changsha 410075, China;

2. Department of Electronic Information Engineering, Changsha Normal University, Changsha 410100, China)

Abstract: Aiming at the increasingly serious power dissipation problem of field programmable gate array (FPGA) caused by their growing integration and speed, a new design method for multiplexers suitable for FPGA was proposed. Based on the phenomenon of the used multiplexers in FPGA containing many idle transistors, the proposed method reduces the leakage power dissipation of idle transistors in multiplexer by using reverse body bias technique. The simulation results show that the leakage power of multiplexers designed with the new method can be reduced by about 28.97% of that of conventionally designed multiplexers while maintaining other performance. In addition, the proposed method can reduce the leakage power dissipation of unused multiplexers in FPGA and further sharply reduce the static power of FPGA.

Key words: low power; multiplexer; reverse body bias technique (RBB); field programmable gate array (FPGA)

现场可编程门阵列(field programmable gate array, FPGA)因其可编程特性好、开发周期短、高性能、低成本等优势,被广泛应用于原型验证、工业控制、计算机硬件、通信、汽车电子、航空航天等领域[1],此外,由于其具有独特的可重构特性,还被认为是构建自适应系统的首选器件[2]。然而,随着集成电路的制造工艺进入纳米阶段,FPGA的设计面临着一系列新的难题,功耗问题就是其中之一。功耗问题不但影响着FPGA的性能、封装、测试以及系统可靠性,还在很大程度上决定着FPGA未来的发展方向。从功耗来源角度看,FPGA芯片的功耗可以分为动态功耗和静态功耗, 在CMOS工艺到达90 nm之前,FPGA的功耗主要由动态功耗构成,约占总功耗的62%以上[3]。近年来,随着集成电路工艺特征尺寸的减小,晶体管的栅氧化层厚度和阈值电压也必须相应的缩小,导致漏电流功耗的指数性增长。当芯片制造工艺到达45 nm时,FPGA的静态功耗已超过动态功耗成为芯片总功耗的决定因素。在FPGA几种主要资源中,多路选择器消耗的静态功耗所占的比例较大,约占FPGA总静态功耗的34%[4],因此,降低FPGA布线资源中多路选择器的泄漏功耗对有效降低FPGA整体静态功耗有着重要的现实意义。

针对FPGA静态功耗问题,国内外已有一些相关的研究,典型的静态功耗优化技术有电源门控技术[5]、双电压技术[6]、反向衬底偏置技术[7]等。电源门控技术通过关断电路的电源降低电路的功耗,该技术最适合应用于移动设备,其主要缺点是需要增加门控晶体管,因此,增加额外硬件开支及增大电路面积是应用电源门控技术时首要考虑的问题。双电压技术是FPGA低功耗设计领域中一种有效常用的方法,该方法可以同时降低电路的动态功耗和静态功耗。由于双电压技术的实现是基于电路中存在非时序关键路这一前提,因此其应用领域有一定的局限性,同时双电压技术也存在增加硬件开支等缺点。反向衬底偏置技术是一种降低漏电功耗的通用方法,已经成功应用于FPGA的静态功耗优化并取得了较好的效果[7]。然而,在以往的研究中,由于对反向衬底偏置技术会造成晶体管延时这一缺陷没有很好的考虑和处理,采用该项技术在降低静态功耗的同时往往会增加电路的延时,导致系统性能急剧下降。针对此问题,本文作者提出了一种适合于FPGA的低功耗多路选择器设计方法。该方法充分考虑了当前FPGA中多路选择器设计存在大量闲置晶体管这一特点,采用反向衬底偏置技术对FPGA中被使用多路选择器内闲置晶体管的泄漏电流进行优化,该方法克服了反向衬底偏置技术在降低静态功耗时增加电路延时的缺陷,在不影响电路性能的前提下有效的降低了FPGA的静态功耗。

1 FPGA中多路选择器结构

典型的FPGA器件主要包含3类基本资源:可编程逻辑块(configurable logic block,CLB)、布线资源和可编程输入/输出模块。可编程逻辑块四周被预制的布线资源通道包围,可编程输入/输出模块分布在FPGA四周,除了上述3种资源以外,通常在FPGA中还包含块RAM、乘法器等可选资源[8]。

在FPGA各种资源中,可编程逻辑块是实现用户功能的基本单元,每个可编程逻辑块包含1个互连开关矩阵和4个SLICEs,其中每个SLICE包括2个查找表(Look-Up-Table,LUT)、2个触发器和一些多路选择器。互连开关矩阵主要由不同长度导线和多个布线开关组成,典型的布线开关结构如图1所示。

图1 FPGA布线开关结构图

Fig. 1 FPGA routing switch structure

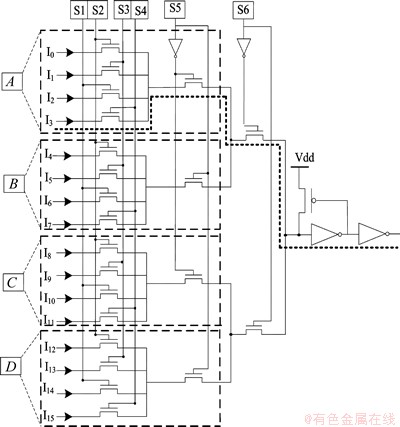

由图1可见:每个布线开关由多路选择器、缓冲器和一些可编程的SRAM单元构成。其中多路选择器是连接各布线轨道和可编程逻辑块的桥梁,其结构对FPGA的性能和功耗都有较大的影响。根据多路选择器所驱动的导线长度不同,FPGA中多路选择器的规模从4选1到30选1不等。图2所示为16选1的多路选择器晶体管级电路结构。

多路选择器的左边是16条输入线,用于连接布线轨道或可编程逻辑块等资源,S1~S6代表6个可编程SRAM单元,通过配置SRAM单元的内容可以从16条输入线中选出1条作为有效输入端,例如,当S1~S6存储单元的存储值为“000100”时,输入线I3被选择中,信号所经过的有效路径如图2中虚线所示。多路选择器的主体部分是传输晶体管,由于NMOS晶体管载流子的迁移效率高,电路速度快,因此,多路选择器中的传输晶体管均采用NMOS晶体管实现。

图2 多路选择器的晶休管级电路结构图

Fig. 2 Multiplexer circuit structure

2 低功耗多路选择器设计方法

2.1 衬底偏置技术

衬底偏置技术基于衬底偏置MOS管的阈值电压可调节特性,通过改变晶体管阈值电压调节晶体管的功耗和性能。衬底偏置NMOS管的截面如图3所示,其中,VBS为体偏置电压;VDS为漏源电压;VGS为栅源电压。与传统的栅驱动电路相似,信号从栅极输入,通过在衬底端和源端加上一个小于PN结导通电的体偏置电压VBS来调节MOS管的阈值电压。

图3 基于衬底偏置的NMOSFET横截面图

Fig. 3 Cross section of a NMOSFET with body bias

衬底偏置技术分为前向衬底偏置技术和反向衬底偏置技术。前向衬底偏置技术通过降低晶体管的阈值电压提高加晶体管的性能,该项技术存在的不足是增加晶体管的静态功耗。反向衬底偏置技术通过调节体偏置电压来增加晶体管的阈值电压最终达到降低晶体管静态功耗的目的,其主要缺点是会引起晶体管的延时增加。

基于衬底偏置技术设计思想,文献[9]设计了一种可编程的阈值电压结构,其实现机理如图4所示。在可编程阈值电压结构中每个晶体管可以通过配置SRAM单元的值确定其所加体偏置电压,从而调节晶体管的阈值电压最终达到提高晶体管的性能或降低晶体管静态功耗的目的。在上述结构中,由于每个晶体管都采用了双阈值结构,因此该结构会带来较大的面积开销。

图4 可编程阈值电压结构实现机理图

Fig. 4 Programmable structure of threshold voltages realization mechanism

2.2 反向衬底偏置技术

当MOS 管的衬底和栅端的电压差VBS≠0 时,MOS管的阈值电压VTH会随之变化。这就是MOS管二级效应中的体效应或背栅效应[10],NMOS 管的阈值电压可以表示为

(1)

(1)

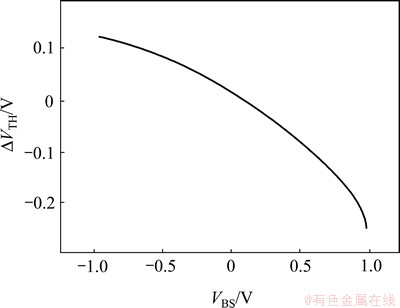

其中:VTH0为VBS=0时的阈值电压;λ为体效应系数; 为表面势。文献[11]对晶体管的阈值电压与体偏置电压的关系进行了研究,其结果如图5所示。从图5可以看出:晶体管的阈值电压和体偏置电压密切相关,并且晶体管的阈值电压随着体偏置电压减小而增大。

为表面势。文献[11]对晶体管的阈值电压与体偏置电压的关系进行了研究,其结果如图5所示。从图5可以看出:晶体管的阈值电压和体偏置电压密切相关,并且晶体管的阈值电压随着体偏置电压减小而增大。

在NMOS晶体管中,泄漏电流主要包括源漏级反偏漏电流(reverse biased junction band to band tunneling, BTBT)、亚阈值泄漏电流(sub-threshold leakage)和栅极漏电流(gate-oxide leakage)3种,其中,亚阈值泄漏电流仍是当前最主要的泄漏电流来源之一[12]。亚阈值泄漏电流是当晶体管的栅源电压小于阈值电压时,源极与漏极之间的沟道中存在的电流,亚阈值泄漏电流可以表示如下[13]:

(2)

(2)

其中:Vt为阈值电压;u为载流子迁移率;n为亚阈值摆幅系数;Cox为单位面积上栅氧电容;VT为热电压,W;L为晶体管的有效宽度和长度。由式(2)可知,亚阈值泄漏电流与晶体管器件的几何特性、工作温度等因素相关。在其他条件不变的情况下,晶体管的亚阈值泄漏电流会随阈值电压的降低呈指数形式增长,增大晶体管的阈值电压是减小晶体管亚阈值泄漏电流一种非常有效的方法。同时,由于晶体管的阈值电压随着体偏置电压减小而增大,因此,可以通过降低晶体管的体偏置电压来增加晶体管的阈值电压,最终达到降低亚阈值泄漏电流的目的,这正是反向衬底偏置技术降低晶体管静态功耗的思想。

图5 阈值电压随体偏置电压改变而变化趋势图

Fig. 5 Trend chart of threshold voltage of NMOSFET varying according to body biasing voltage

反向衬底偏置技术作为一种有效的静态功耗优化方法已被成功的应用于FPGA布线资源低功耗设计中[7]。与电源门控技术和双电压技术相比,由于反向衬底偏置技术实现时只需增加少量的导线,因此具有易实现、增加电路面积小等优点。然而,由于反向衬底偏置技术的本质是通过增加晶体管的阈值电压来降低其泄漏电流,而阈值电压的增加将引起较大的晶体管延时,因此反向衬底偏置技术的最大缺点是将引起电路延时增加。在FPGA中,电路的延时大部分是由布线资源的延时造成的,布线开关中的多路选择器作为布线资源核心部分,其结构直接影响FPGA器件的性能和功耗。因此,文献[7]将反向衬底偏置技术应用于FPGA布线资源功耗优化时,虽然该项技术在降低46%静态功耗的同时还具有增加电路面积小、易实现等优点,但其主要问题是引起较大的晶体管延时,导致FPGA器件性能急剧下降。为了解决上述矛盾,本文提出了一种适合于FPGA的低功耗多路选择器设计方法。

2.3 低功耗多路选择器设计

与专用集成电路相比,FPGA最大的特点是具有可编程的特性,用户通过编程SRAM单元的内容设计实现所需的各种电路,当FPGA完成配制后,所制定的电路一般不再改变。分析完成配制后的FPGA结构可以发现,在FPGA布线开关中每个被使用的多路选择器只有1条有效的输入线和1条被使用的有效路径,并且在有效路径之外的晶体管一直处于闲置状态。从图2可以看出:在整个多路选择器中只有3个位于有效路径上的晶体管处于工作状态,其余19个在有效路径外的晶体管一直处于闲置状态,这些闲置的晶体管同样要消耗大量的漏电功耗。针对上述问题,本文提出了一种低功耗多路选择器设计方法。该方法的主要思想是:将布线开关中多路选择器分成若干个区域,每个区域拥有各自实现反向衬底偏置技术的控制电路,具体实现时仅对处于闲置状态分区中的晶体管采用反向衬底偏置技术降低其静态功耗,而有效路径所经过分区中的晶体管仍然维持其原来的状态,确保电路正常工作。下面以16选1的多路选择器为例阐述该方法实现的具体步骤。

步骤(1),将多路选择器分成4个区,并分别用A,B,C,D表示,分区结果如图6所示。

图6 分区后的多路选择器晶体管级结构图

Fig. 6 Structure of partition multiplexer transistor circuit

步骤(2),以区为单位,为每个分区中的晶体管配备实现反向衬底偏置技术的电路,具体实现方式如图7所示。图中,S代表SARM存储单元,另外每个分区增加1个SRAM单元,通过配置该SRAM单元的值就可以给区中的晶体管加上体偏置电压VBS,用于增大晶体管的阈值电压。

步骤(3),确定多路选择器中未被使用的区。实现这一步主要使用JBits工具,JBits是Xilinx 公司提供的一组用Java 语言实现API函数,调用这些函数可以实现对FPGA 的配置位流文件按位回读和定位修改等操作[14]。确定多路选择器中未被使用的区具体操作分为2步:1) 基于ISE的FPGA开发流程主要包括转换、映射、布局布线等几个主要阶段,在布局布线阶段产生的NCD文件中包含当前设计的全部物理实现信息。用XDL工具用于将布局布线产生的NCD文件转变成以文本的方式表示的XDL文件,从XDL文件可获得FPGA中各种资源详细的使用情况[15],从而确定在该应用设计中被使用的多路选择器。2) 用JBits工具获取和每个被使用多路选择器相关联的SRAM单元存储值,并根据这些SRAM单元的存储值就可确定有效的输入线和信号所经过的有效路径所在的区。以图6为例,如果S1~S6的存储值为“000100”,则可以确定在这个多路选择器中,有效信号只经过了A区,剩下的B,C和D 3个分区均未被使用。

图7 以区为单位的反向衬底偏置技术实现图

Fig. 7 Implementation of reverse body-bias technology in district unit

步骤(4),降低多路选择器中未被使用区内闲置晶体管的功耗。当确定多路选择器中未被使用的分区后,就可以采用反向衬底偏置技术降低未被使用区内所有晶体管的泄漏电流,即通过配制图7中SRAM单元,使该分区内的晶体管加上产生高阈值电压的体偏电压。随着阈值电压的增加,晶体管的亚阈值泄漏电流被有效地抑制,因此,可大幅度降低晶体管的静态功耗。同时,有效路径所经过分区中的所有晶体管保持原状态不变,确保了电路的正常工作。以图6为例,由于有效信号的路径只经过了A区,因此,B,C和D 3个区中的晶体管都可采用反向衬底偏置技术降低其静态功耗,A区中的晶体管则保持其原来状态,保证了电路的正常工作。

从以上优化方法的实施步骤可以看出:由于优化的对象只局限于多路选择器中闲置的晶体管,因此,该方法克服了反向衬底偏置技术在降低泄漏功耗时将造成电路延时的缺陷,发挥了反向衬底偏置技术优势。在不影响电路性能的情况下,该方法可以大幅降低多路选择器中的静态功耗。

3 实验与结果分析

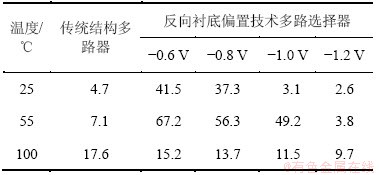

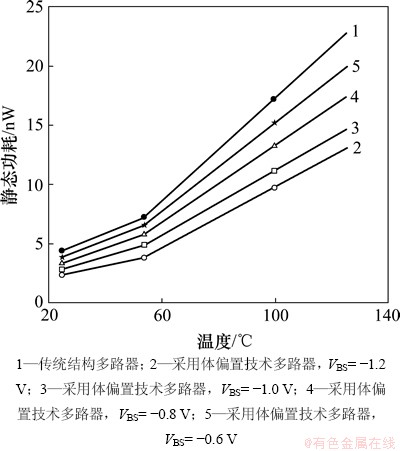

基于TSMC 0.18 μm CMOS工艺,电源电压为1.8 V,在HSPICE仿真平台下对多路选择器电路优化前后的静态功耗进行模拟分析。表1所示为体偏置电压分别在-0.6,-0.8,-1.0和-1.2 V时新型结构多路选择器和传统结构多路选择器在不同温度下静态功耗。图8所示为多路选择器结构优化前后整体静态功耗的量化对比。

从表1和图8可以看出:无论是在25 ℃还是在100 ℃的条件下,采用反向衬底偏置技术后的多路选择器的静态功耗都有较大的降幅。在100 ℃时,4种不同体偏置电压条件下多路选择的静态功耗平均值约为12.5 nW,与传统结构多路选择器的静态功耗17.6 nW相比,降低了约28.97%。此外,从图8还可以看出:在相同温度的条件下,随着体偏置电压降低多路选择器的静态功耗也呈下降趋势,即负偏压越低静态功耗优化效果越明显。

表1 多路选择器优化前后的静态功耗

Table 1 Static power of multiplexer before and after optimization 静态功耗/nW

图8 多路选择器优化前后静态功耗的对比

Fig. 8 Comparison of static power of multiplexer before and after optimization

在FPGA的应用设计中,为了确保FPGA布局、布线及映射的灵活性通常有相当一部分资源未被使用,这些未被使用的资源要消耗大量的静态功耗,文献[4]研究表明,当FPGA中可编程逻辑块资源的利用率为50%时,FPGA中未被使用的资源所消耗的静态功耗约占FPGA总静态功耗的56%,在这些未被使用的资源中存在大量闲置的多路选择器,这些闲置的多路选择器同样可以采用本文所提出的方法进行静态功耗优化,具体实现步骤是:

(1) 确定FPGA中未被使用的多路选择器。与前面提到的方法相同,用Xilinx公司的ISE工具对所设计的项目进行综合、映射、布局布线产生NCD文件。再用XDL工具将布局布线产生的NCD文件转变成以文本的方式表示的XDL文件,根据 XDL文件的内容确定该设计中FPGA内未被使用的多路选择器。

(2) 对未被使用的多路选择器中所有晶体管采用反向衬底偏置技术进行静态功耗优化。由于未使用的多路选择器中没有信号经过,因此可以将这些闲置的多路选择器中所有的晶体管都加上体偏置电压,增加阈值电压低其静态功耗。

由于在FPGA的布线开关中存在大量闲置的多路选择器,因此,当该方法应用于FPGA中闲置多路选择器功耗优化时可以大幅降低FPGA的静态功耗。

4 结论

(1) 提出了一种适合于FPGA的低功耗多路选择器设计方法,该方法根据完成配制后的FPGA中被使用多路选择器的结构特点,采用反向衬底偏置技术对FPGA中被使用的多路选择器泄漏功耗进行优化。实验结果表明,该方法在保持电路性能的前提下,以少量的面积开销为代价,可大幅度降低多路选择器的低静态功耗。

(2) 充分考虑了完成配制后的FPGA中多路选择器内绝大部分晶体管处在闲置状态这一特点,提出了只针对FPGA中被使用的多路选择器内闲置晶体管的泄漏电流进行优化的方法,该方法解决了反向衬底偏置技术在降低静态功时增加电路延时的缺陷,同时也提出了一种根据FPGA中资源的使用情况决定其功耗优化方法的思路。

(3) 本文所提出的方法不但可以降低FPGA中被使用多路选择器的静态功耗,而且可降低FPGA中未被使用的多路选择器的静态功耗。由于在基于FPGA应用设计中通常包括大量闲置的多路选择器,因此,当将该方法应用于FPGA中未被使用的多路选择器时,可以进一步大幅度降低FPGA中的静态功耗。

参考文献:

[1] 杨海钢, 孙嘉斌, 王慰. FPGA器件设计技术发展综述[J]. 电子与信息学报, 2010, 32(3): 714-726.

YANG Haigang, SUN Jiabin, WANG Wei. An overview to FPGA device design technologies[J]. Journal of Electronics & Information Technology, 2010, 32(3): 714-726.

[2] Savage J, Savage R. Adaptive FPGA-based robotics state machine architecture derived with genetic algorithms[C]// Proceedings of the ACM/SIGDA 20th International Symposium on Field Programmable Gate Arrays. California: ACM Press, 2012: 22-24.

[3] Tuan T, Rahman A. A 90-nm low-power FPGA for battery-powered applications[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2007, 26(3): 296-300.

[4] Tuan T, Lai B. Leakage power analysis of a 90 nm FPGA[C]// Proceedings of the IEEE Custom Integrated Circuits Conference. San Jose, CA: IEEE Press, 2003: 57-60.

[5] Naveena K, Kirthika N. A low power asynchronous FPGA with power gating and LEDR encoding[J]. Bonfring International Journal of Power Systems and Integrated Circuits, 2012, 2(1): 68-72.

[6] Lin Y, He L. Statistical dual-Vdd assignment for FPGA interconnect power reduction[C]// Proceedings of the Conference on Design, Automation and Test in Europe. San Jose, CA: EDA Consortium, 2007: 636-641.

[7] Leming G V. Low-power FPGA routing switches using adaptive body biasing technique[J]. IEEE International Midwest Symposium on Circuits and Systems, 2009: 447-450.

[8] Hasan M, Kureshi A K, Arslan T. Leakage reduction in FPGA routing multiplexers[C]// IEEE International Symposium on Circuits and Systems. Taipei: IEEE Press, 2009: 1129-1132.

[9] Kawanami T, Hioki M, Matsumoto Y. Optimal set of body bias voltages for an FPGA with field-programmable Vth components[C]// Proceedings of the IEEE International Conference on Field Programmable Technology. Bangkok: IEEE Press, 2006: 329-332.

[10] Hassan H, Anis M, Elmasry M. Input vector reordering for leakage power reduction in FPGAs[J]. IEEE Trans Comput Aided Design, 2008, 27(9): 1555-1564.

[11] Lee Y, Kim T. A fine-grained technique of NBTI-aware voltage scaling and body biasing for standard cell based designs[C]// 16th Asia and South Pacific Design Automation Conference. Yokohama: IEEE Press, 2011: 603-608.

[12] Salami B, Zamani M S. VMAP: A variation map-aware placement algorithm for leakage power reduction in FPGAs[C]// 14th Euromicro Conference on Digital System Design. Finland: IEEE Press, 2011: 81-87.

[13] Kursun V, Friedman E G. 多电压CMOS电路设计[M]. 马俊婷, 郭志川, 孙鹏, 译. 北京: 机械工业出版社, 2006: 24-26.

Kursun V, Friedman E G. Multi-voltage CMOS circuit design[M]. MA Junting, GUO Zhichuan, SUN Peng, trans. Beijing: China Machine Press, 2006: 24-26.

[14] Das N. BIST to diagnosis delay fault in the LUT of cluster based FPGA[J]. International Journal of Information and Electronics Engineering, 2012, 2(2): 269-273.

[15] Jevtic R, Carreras C. Power measurement methodology for FPGA devices[J]. IEEE Transactions on Instrumentation and Measurement, 2011, 60(1): 237-247.

(编辑 赵俊)

收稿日期:2013-06-13;修回日期:2013-09-16

基金项目:国家自然科学基金重点资助项目(61134006)

通信作者:李列文(1974-),男,湖南常德人,博士研究生,从事FPGA低功耗设计技术研究;电话:13787143246;E-mail: lilw168@126.com